GPU 중심 AI 시대, CPU 전략 ‘더 많은 코어·더 강한 코어’ [테크리포트]

||2026.02.06

||2026.02.06

생성형 인공지능(AI) 시대의 시작과 함께 최근 몇 년간 인공지능(AI) 인프라에서 화제의 중심은 ‘그래픽처리장치(GPU)’가 차지해 왔다. 더 크고 정교한 모델을 더 빨리 구축해 시장에 선보이는 경쟁에서 GPU는 전통적인 컴퓨팅의 중심이었던 중앙처리장치(CPU)보다 훨씬 빠른 처리가 가능했기 때문이다. 하지만 CPU는 여전히 컴퓨터 구조에서 없어서는 안 될 존재다. 최근 AI 생태계의 추론 중심으로의 변화와 ‘가속 컴퓨팅’의 다변화에 따라 CPU 수요도 늘고 있다.

현재 전 세계 컴퓨팅 시장의 중심에는 인텔과 AMD로 상징되는 ‘x86’ 아키텍처가 있다. 하지만 같은 x86 생태계 속에서도 인텔과 AMD의 프로세서 설계 방향은 서로 다른 모습이다. 현재 인텔은 좀 더 ‘워크로드 특화’로, AMD는 좀 더 ‘범용적’인 설계를 선보이는 점이 눈에 띈다. 이러한 CPU 설계의 방향성은 어느 한 쪽의 우열을 따지기보다는 상황에 따른 ‘선택’의 문제로 바라봐야 한다.

‘워크로드 특화’ 지향하는 차세대 CPU 설계

본격적인 AI 시대 이후 인프라 시장에서 모든 관심이 GPU로 이동한 것처럼 보였지만 CPU는 여전히 중요한 위치에 있다. 현재 시스템 구조에서는 GPU만으로 모든 워크로드를 처리할 수 없고, 여전히 CPU는 시스템의 모든 구성 요소를 연결, 제어하는 중심이다. GPU 성능이 중요하게 여겨지는 AI 워크로드에서도 데이터 준비 등 작업의 상당 부분은 CPU가 활용된다. GPU만으로는 시스템을 구동할 수 없지만, CPU만 있어도 AI 연산은 처리할 수 있다.

이러한 CPU의 위상 변화는 최근 인텔과 AMD의 실적 발표에서도 찾아볼 수 있다. 립부 탄 인텔 CEO는 최근 실적 발표에서 “서버용 프로세서 수요가 늘고 있다”고 언급했고, 인텔의 DCAI(Data Center & AI Group) 사업부 실적 또한 성장세를 기록했다. 서버용 프로세서에 대한 수요 증가는 대형 클라우드 사업자들의 인프라 확장과 기업들의 노후 인프라 교체, 엣지 AI에 대한 수요 증가 등 다양한 요소들이 복합적으로 작용한 결과로 해석된다.

모든 AI 워크로드에 GPU가 효과적인 것도 아니다. 가상화 기반으로 구현된 엣지 서버에서는 여러 가지 워크로드가 동시에 운영되고, 필요한 성능을 갖출 수 있다면 GPU 없이 CPU만으로 AI 워크로드를 처리하는 편이 시스템 전반적인 효율에서 더 나은 선택이 될 수 있다. 실제 제법 많은 기업들이 CPU만으로도 실용적인 AI 환경을 구축하고 있다. 지난해 AMD의 ‘어드밴싱 AI 2025’에서는 우버(Uber)가 이러한 사례를 발표한 바 있다.

전통적인 기업 환경의 워크로드에서 대규모 클라우드 사업자들의 AI 인프라에 이르기까지 CPU가 다뤄야 할 워크로드의 유형도 더욱 다양해졌다. 이에 접근하는 인텔과 AMD 양 사의 전략은 비슷한 듯 하면서도 사뭇 다르다. 인텔은 좀 더 근본적인 ‘워크로드 최적화’로 접근해 성능과 밀도 중심의 프로세서를 아키텍처 차원에서 따로 마련했다. 반면 AMD는 좀 더 다양한 워크로드를 다룰 수 있는 범용성을 기반으로 코어 수를 확장하는 전략이 특징이다.

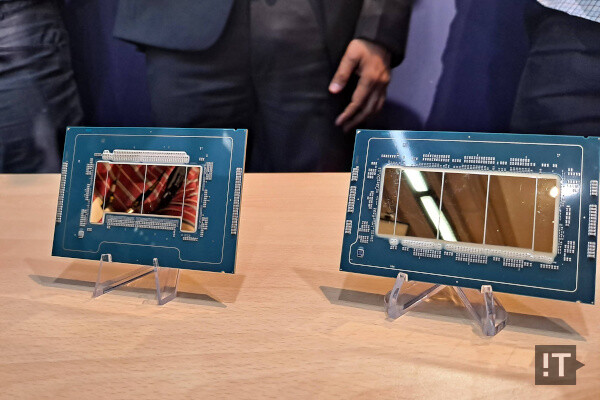

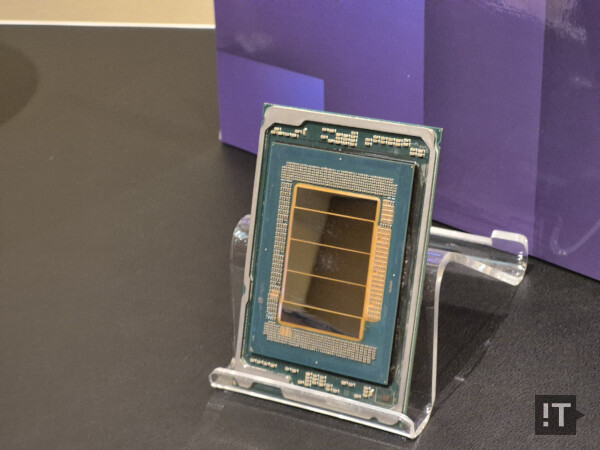

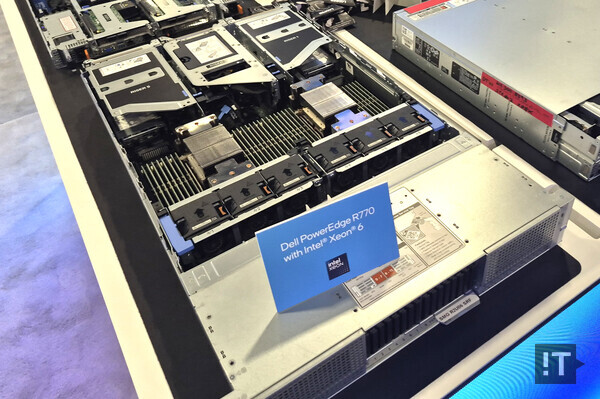

인텔의 최신 세대 프로세서 ‘제온 6’ 제품군은 이러한 ‘워크로드 특화’ 설계가 적극적으로 반영됐다. ‘레드우드 코브(Redwood Cove)’ P-코어 기반으로 최대 128코어 구성을 제공하는 제온 6 P-코어 제품군은 코어 내부적으로도 전통적인 x86 코어의 범위를 넘어선 ‘가속기’들이 통합된 점이 특징이다. 이러한 아키텍처적 특징은 개별 코어를 더 크게 만들었고, 가속기의 활용 여부에 따라 성능 평가가 달라지는 이유가 됐다.

제온 6의 P-코어 제품군에서 주목할 만한 기능으로는 이미 4세대 제온 스케일러블 프로세서에서 도입된 AMX(Advanced Matrix Extensions)가 있다. X86 명령어 체계의 확장 명령어 형태로 제공되는 이 AMX는 AI에 많이 사용되는 행렬 연산에 최적화돼 기존 AVX-512 기반 처리 대비 8배 많은 연산을 수행할 수 있다. 잘만 사용하면 엔트리급 GPU 없이 CPU만으로도 실용적인 AI 연산 성능과 범용성을 모두 얻을 수 있다. 이외에도 제온 6 계열 프로세서와 플랫폼에는 데이터 압축이나 이동, 암호화 등을 위한 가속기가 내장돼 있다.

제온 6 E-코어 제품군은 이와 반대로 철저히 ‘범용성’과 ‘밀도’에 초점을 맞췄다. 이에 코어 면적이 많이 필요한 AVX도 256비트 AVX2까지만 지원하고 구조도 단순화한 E-코어를 활용해 멀티 코어를 넘어선 ‘매니 코어’를 구현했다. 현재 제온 6 E-코어 ‘시에라 포레스트’는 최대 144코어를 제공하며 차세대 ‘클리어워터 포레스트’는 288코어 구성까지 제공할 계획이다. 이는 x86 계열에서의 코어 수 경쟁은 물론, Arm 아키텍처 기반 프로세서와의 경쟁에서도 숫자로 압도 가능한 수준이다.

AMD의 관점은 인텔의 두 프로세서 사이에서 ‘범용성’을 기반으로 더 많은 코어를 탑재하는 데에 무게가 실려 있다. 현재 AMD의 ‘젠 5’기반 에픽 ‘튜린(Turin)’은 ‘젠 5’ 기반에서 CCD(Core Complex Die) 16개를 사용해 128코어를, ‘젠 5c’기반에서는 12개 CCD로 최대 192코어를 제공한다. AMD의 고성능 ‘젠 5’와 고밀도 ‘젠 5c’는 같은 아키텍처 기반에서 사양 조절과 공정 특성 최적화로 파생되는 관계로, 인텔의 P-코어와 E-코어 만큼의 차이는 나지 않는다. 명령어 지원도 AVX-512 수준으로, 인텔의 P-코어와 E-코어 사이에 위치한다.

이러한 설계 특성의 차이는 고객이 바라보는 관점에 따라 평가가 달라진다. 다양한 워크로드가 혼재하는 대규모 클라우드 사업자의 인프라에서는 표준적인 기능과 성능을 갖춘 코어를 다수 갖춘 AMD 에픽이나 인텔의 E-코어 기반 프로세서가 매력적이다. 범용 클라우드 환경은 컴퓨트와 스토리지, 네트워크까지 범용 프로세서를 사용한 ‘소프트웨어 정의’ 구조로, 코어의 개성보다는 적당한 범용성에 더 많은 코어를 집적하는 쪽이 유리하기 때문이다.

하지만 워크로드 유형을 어느 정도 특정할 수 있다면 인텔의 P-코어 기반 프로세서의 경쟁력이 높다. 엣지 AI나 데이터베이스, 스토리지와 네트워크 어플라이언스 같은 영역이 대표적이다. 이에 스토리지나 5G 기지국 등의 경우 프로세서와 플랫폼에 하드웨어 가속 기능이 갖춰진 인텔의 플랫폼을 사용하는 경우가 흔하다. 대규모 클라우드 환경에서도 특정 목적을 위한 인프라 구성에 효과적이다.

한편, 일반 사용자용 프로세서에서 흔한 ‘하이브리드’ 코어 구성은 서버용 프로세서에서는 활용될 계획이 없는 모습이다. 이는 가상화 기반의 데이터센터용 워크로드에서 각 코어별 작업을 적절히 분배하기 까다롭고, 제품 디자인 차원에서도 각 코어별 수량을 정하기 어렵기 때문이다. 이에 대해 키유르 하라리(Keyur Halari) 인텔 네트워크 및 엣지 그룹 제온 제품 라인 및 시스템 디렉터는 지난 9월 IT조선과의 인터뷰에서 “데이터센터에서 하이브리드 코어 구성은 적절한 스케줄링을 맞추기 쉽지 않다”고 언급한 바 있다.

코어 수 경쟁 속 각자의 ‘시장 최적화’ 방향성

지금까지 몇 년간 서버용 CPU 시장에서 개별 코어에서는 인텔이, 코어 수에서는 AMD가 앞서는 모습을 보여 왔다. 이는 AMD가 초창기 에픽 프로세서부터 멀티칩 패키징을 사용해 코어 수를 늘리기 좋은 구조였기 때문이다. 하지만 현재 세대에는 이 차이가 거의 없어졌다. 인텔 또한 타일 구조 기반에서 고급 패키징 기술을 통해 코어 수 경쟁을 빠르게 따라잡았다. 현 세대에서는 주력인 고성능 코어 제품 기준으로는 양 사가 동등하고, 밀도 중심의 제품에서는 아직 AMD가 앞서 있는 상태다.

차세대 제품군에서는 이 상황이 바뀔 전망이다. 상반기 공식 출시 예정인 인텔의 차세대 E-코어 기반 제온 6+ 프로세서 ‘클리어워터 포레스트(Clearwater Forest)’는 타일 구조와 고급 패키징 기술을 활용해 최대 288코어 구성을 선보여, 코어 수 경쟁에서 AMD는 물론 Arm 아키텍처 기반 매니 코어 프로세서보다도 코어 수에서 우위에 설 것으로 보인다.

하반기에는 양 사의 차세대 서버용 프로세서가 모습을 드러낼 것으로 기대된다. AMD는 차세대 아키텍처 ‘젠 6’ 기반의 에픽 ‘베니스(Venice)’ 시리즈 프로세서를 올해 선보일 것이라고 예고한 바 있다. AMD는 ‘베니스’가 최대 256코어 구성을 제공할 것이라 예고했는데, 기존 ‘튜린’ 시리즈를 볼 때 256코어 구성은 고밀도 ‘젠 6c’ 기반 프로세서에서 제공될 것으로 보인다. 이 경우 코어 수 경쟁에서는 일단 인텔의 ‘클리어워터 포레스트’가 한 발 앞서는 모습이 될 전망이다.

인텔은 기존 제온 6 ‘그래나이트 래피즈’의 후속인 ‘다이아몬드 래피즈’를 하반기 선보일 것으로 알려졌다. 지금까지 알려진 바로는 ‘팬서 코브’ 아키텍처 기반의 P-코어 192개 구성과 현재의 12채널 메모리보다 좀 더 확장된 16채널 메모리 컨트롤러를 제공한다. 명령어 지원에서도 AVX10 체계 지원 등의 확장이 예고되고 있다. 립부 탄 인텔 CEO는 최근 실적 발표에서 “다이아몬드 래피즈의 16채널 메모리 컨트롤러 구성을 빠르게 출시하기 위해 노력하고 있다”고 언급했다.

한편, 인텔은 최근 실적 발표에서 지금까지 별도로 언급되지 않았던 ‘다이아몬드 래피즈’의 후속 프로세서로 코드명 ‘코랄 래피즈(Coral Rapids)’를 언급했다. 이 프로세서는 현 세대 아키텍처에서 제외된 SMT(Simultaneous Multithreading) 기술이 적용될 것으로 알려졌다. 인텔 프로세서에서 ‘하이퍼스레딩(Hyper-Threading)’으로 사용된 SMT 기술은 코어당 멀티스레딩 성능을 30% 정도 향상하지만 최근 세대에서는 효율과 보안 문제 등으로 제외됐다.

서버 시장에서 특정 목적을 위한 ‘특화형’ 프로세서도 주목된다. 인텔과 엔비디아는 지난 9월 양 사의 기술을 결합한 제품을 공동 개발하기로 발표한 바 있다. 이 발표를 통해 인텔의 서버용 제온 프로세서에 엔비디아의 ‘NV링크(NVLink)’ 연결 기술이 적용된 커스텀 칩이 나올 전망이다. 립부 탄 인텔 CEO도 최근 실적 발표에서 이 제품에 대해 언급했다. 기존 인텔 프로세서는 외부의 프로세서와 UPI(Ultra Path Interconnect) 인터페이스 기술을 통해 직접 연결할 수 있는데, 커스텀 칩에서는 이 UPI를 NV링크로 바꾸는 형태다.

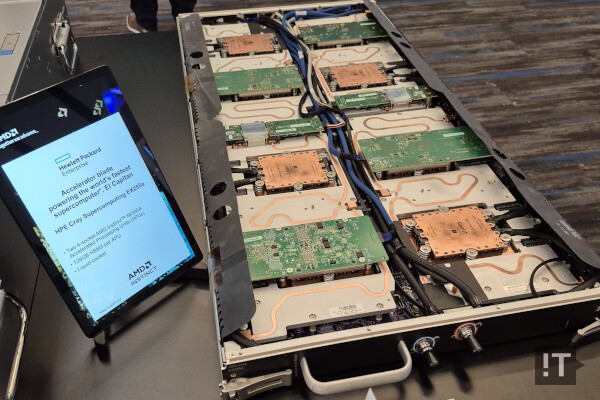

이러한 커스텀 CPU는 현재 엔비디아의 ‘슈퍼칩’ 기반 시스템에서 엔비디아의 Arm 코어 기반 자체 프로세서를 대체하는 옵션으로 활용될 것으로 전망된다. 현재 엔비디아의 슈퍼칩은 하나의 보드 모듈 위에 두 개의 GPU와 한 개의 CPU가 NV링크로 연결되는 형태로, 적절한 NV링크 인터페이스가 있다면 프로세서를 교체하는 것도 가능하다. AMD 또한 차세대 ‘헬리오스’ 랙스케일 솔루션에서 에픽 프로세서와 인스팅트 MI400 시리즈 GPU를 UA링크(UALink)를 사용해 연결할 계획이다.

단일 프로세서를 넘어 ‘단일 패브릭’에 CPU와 GPU, HBM까지 구성되는 확장형 처리장치(XPU, eXtended Processing Unit) 콘셉트의 제품도 주목된다. 이러한 형태의 제품은 이미 AMD가 인스팅트 MI300A로 구현한 바 있는데, CPU-GPU-메모리 간 고속 데이터 전송과 효율이 강점이다. 하지만 AMD는 MI300A 이후 후속 제품군인 MI350, MI400 제품에서는 이러한 콘셉트의 제품을 발표하지 않았다. ‘헬리오스’ 랙스케일 솔루션은 이보다는 엔비디아의 슈퍼칩 기반 NVL72 솔루션과 유사한 형태다.

인텔도 이러한 XPU 콘셉트의 제품을 꾸준히 준비하는 모습이다. 이미 지난 2021년에 언급돼 2025년을 목표로 준비한 ‘팔콘 쇼어(Falcon Shore)’는 결국 취소됐지만 후속 ‘재규어 쇼어(Jaguar Shore)’는 여전히 남아 있는 모습이다. 팔콘 쇼어와 재규어 쇼어는 단일 프로세서 제품에 EMIB(Embedded Multi-die Interconnect Bridge), 포베로스 등 다양한 고급 패키징 기술을 사용해 CPU와 GPU, HBM, 다양한 형태의 가속기를 조합하게 된다.

립부 탄 인텔 CEO는 최근 실적 발표에서 “우리는 지난 몇 분기 동안, 향후 몇 달간 더 구체화될 수 있을 광범위한 AI 및 가속기 전략을 개발해 왔다. 여기에는 고정 기능 및 프로그래밍 가능한 가속기 IP를 x86 CPU와 통합하는 혁신적 옵션이 포함될 것”이라고 밝혔는데 이는 ‘재규어 쇼어’를 의미하는 내용으로 보인다. 인텔의 패키지 기술 로드맵에서도 2028년까지 EMIB를 사용해 12배 이상의 레티클(Reticle) 크기와 24개 이상의 HBM을 단일 패키지로 연결하는 대형 패키징을 지원할 계획인데, XPU 제품에서 가장 먼저 사용될 것으로 전망된다.

권용만 기자

yongman.kwon@chosunbiz.com

고객님만을 위한 맞춤 차량